1.1. Hukum

Komunitatif Untuk Gerbang Logika AND

Hukum Komutatif Untuk Gerbang

Logika AND Gerbang OR dengan 2 masukan tertentu, yaitu A dan B, dapat

dipertukarkan tempatnya dan dapat merubah urutan sinyal-sinyal masukan.

Perubahan tersebut tidak akan mempengaruhi keluarannya. Dalam hukum persamaan

Boolean hal ini dapat ditulis sebagai berikut : A . B = B . A = Y

1.2. Hukum

Komutatif Untuk Gerbang Logika OR

Hukum

komutatif aljabar boolean memiliki kesamaan degan aljabar biasa. Berikut ini

akan kita lihat pemakaian hukum komutatif dalam gerbang-gerbang logika Hukum

Komutatif Untuk Gerbang Logika OR Gerbang OR dengan 2 masukan tertentu, yaitu A

dan B, dapat dipertukarkan tempatnya dan dapat merubah urutan sinyal-sinyal

masukan. Perubahan tersebut tidak akan mempengaruhi Dalam hukum persamaan

Boolean hal ini dapat ditulis sebagai berikut : A + B = B + A = Y

2.1. Hukum

Asosiatif Untuk gerbang OR

Hukum

Asosiatif untuk Gerbang Logika OR Gerbang OR dengan 2 masukan tertentu, yaitu A

dan B, dapat dikelompokan tempatnya dan diubah urutan sinyal-sinyal masukannya.

Perubahan tersebut tidak akan mengubah keluarannya. Dalam hukum persamaan

Boolean ditulis sebagai berikut: A + ( B+ C) = ( A + B ) + C Pada hakekatnya

cara pengelompokan variabel dalam suatu operasi OR tidak berpengaruh pada

keluarannya. Artinya keluarannya akan tetap sama dengan : Y = A + B + C

Perhatikan gambar berikut

2.2. Hukum

Asosatif Untuk AND

Hukum

Asosiatif untuk Gerbang Logika AND Gerbang AND dengan 2 masukan yaitu yaitu A

dan B, dapat dikelompokan tempatnya dan diubah urutan sinyal-sinyal masukannya.

Perubahan tersebut tidak akan mengubah keluarannya. Dalam hukum persamaan

Boolean ditulis sebagai berikut: A. (B . C ) = ( A . B ) .C = Y

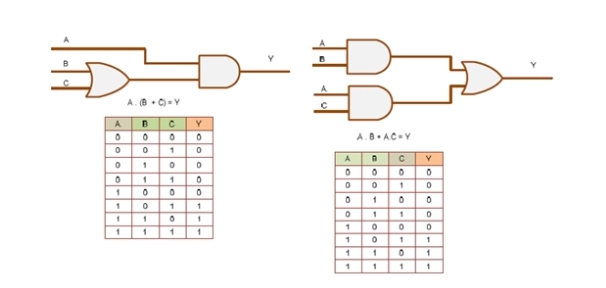

Gerbang

AND dan OR dengan masukan tertentu, yaitu A, B¸dan C, dapat disebarkan

tempatnya, dan dapat dirubah urutan-urutan sinyal-sinyal masukannya. Perubahan

tersebut tidak akan mengubah keluarannya. Dalam persamaan boolean ditulis

sebagai berikut : A. ( B + C ) = AB + AC

Sifat-sifat Khusus Ajabar Boole

Sifat

Khusus dalam operasi Gerbang OR

– Kaidah Pertama : A + 0 = A

– Kaidah Kedua : A + 1 = 1

– Kaidah Ketiga : A + A = A

– Kaidah Keempat :A+Anot=

Sifat Khusus dalam operasi Gerbang AND – Kaidah

Pertama : A . 0 = 0

– Kaidah Kedua : A.1 = A

– Kaidah Ketiga : A . A = A

– Kaidah Keempat : A . ?

Sifat Absorpsi

Untuk membuktikan sifat atau

teorema ini perhatikan persamaan berikut :

Kedua rangkaian logika

diatas memiliki keluaran yang sama untuk kondisi masukan A dan B yang sama.

Sifat Reduksi A + AB = A Untuk membuktikan sifat atau teorema ini perhatikan

persamaan berikut:

Kedua rangkaian logika

diatas memiliki keluaran yang sama untuk kondisi masukan A dan B yang sama.

Sifat Reduksi A + AB = A Untuk membuktikan sifat atau teorema ini perhatikan

persamaan berikut:

Sifat

Absorpsi

Untuk

membuktikan sifat atau teorema ini perhatikan persamaan berikut :

Teorema

De Morgan – Teorema Pertama

Persamaan

gerbang logika NOR :

Rangkaian

logika 2 masukan yang di “NOT” kan dan kemudian hubungkan ke gerbang AND

Dari

rangkaian diatas dapat ditulis persamaan aljabar boolean sebagai berikut :

Karena

kedua rangkaian diatas menghasilkan masukan dan keluaran yang ekivalen atau sama

maka dapat dinyatakan sebagai berikut :

Teorema

Kedua

Persamaan

gerbang logika NAND :

Rangkaian

yang terdiri dari logika NOT dan gerbang logika OR :

Rangkaian

diatas dapat dituliskan ke dalam persaman berikut :

Kedua

rangkaian logika diatas memiliki kesamaan sifat atau dapat dikatakan keduanya

ekivalen sehingga dapat dibuktikan teorema de morgan sesuai dengan kedua

persamaan di atas.

B.RANGKAIAN

GERBANG KOMPLEK

Desain gerbang logika kompleks :

- jaringan P menggambarkan luaran

- Le réseau N tire la sortie à 0

- Jaringan N et P komplementer

- satu dari dua jaringan driven

C.DASAR-DASAR

FLIP FLOP D,RS,JK

A. Flip Flop RS (Reset Set Flip Flop)

Dengan menggunakan gabungan gerbang – gerbang

logika menjadi suatu gerbang logika kombinasional dan kemudian diumpan balikkan.

Lalu dapat dibangun suatu rangkaian logika yang dapat menyimpan data. Rangkaian

logika ini disebut dengan piranti atau rangkaian flip flop. Flip Flop ini adalah

elemen memori terkecil yang dapat menyimpan data sebesar 1 bit, yaitu 0 atau 1.

Flip Flop juga merupakan piranti yang memiliki dua keadaa stabil. Piranti ini

akan tetap bertahan padansalah satu keadaan itu sampai ada pemicu yang

membuatnya berganti keadaan.

Flip Flop dengan penahan NOR dibangun dengan

mengggunakan rangkaian terpadu (IC). Flip Flop yang dibangun dengan menggunakan

gerbang logika NOR dinamakan penahann NOR.

Penahan NOR dapat dinyatakan kembali

dengan teorema De morgan, sehingga kita dapatkan rangkaian penahan yang lain

tetapi dengan fungsi yang sama

Flip Flop SR dengan gerbang NOT dan

AND

Masukkan R dalam keadaan 0 dan S dalam keadaan

1 memberikan keadaan SET. Sedangkan apabila R dalam keadaan 1 dan S dalam

keadaan 0 akan memberikan keadaan RESET. Namun saat SET dan RESET dalam keadaan

1, akan terjadi keadaan pacu. Oleh karena itu kita harus menghinari keadaan R

dan S dalam keadaan 1. Sedangkan Saat S dan R dalam keadaan 0, tidak terjadi

perubahan.

Prinsip Kerja Penahan NOR.

1. Pengujian Rankaian.

Apabila S rendah (0),

maka keluaran Q akan rendah, walaupun keadaan R dirubah mejadi tinggi maupun

rendah, maka Q tetap rendah.

2. Keadaan SET.

Apabila S dalam keadaan

1 (tinggi) keluaran Q akan 1 (tinggi). dan S hanya sekali memberikan pulsa, dari

keadaan 0 menjadi 1. Sesudah itu jika keadaan S berubah-rubah , keluaran Q akan

tetap 1.

3. Keadaan RESET.

Pada keadaan ini,

keluaran Q tetap 1 (tinggi) apapun yang terjadi pada S. Cara menurunkan atau

mengubah keadaan dengan menurunkan pulsa dari 1 menjadi 0 adalah dengan cara

mengaktifkan R. Begitu R berubah keadaannya dari 0 menjadi 1 maka seketika itu

juga keluaran Q akan menjadi 0 (rendah). Sesudah itu, apapun yang terjadi pada

masukan R, flip flop tidak akan menganggapi.

Saat ingin mengubah

keadan keluaran Q lagi maka S harus diberi pulsa kembali, maka keluaran Q akan

menjadi 1. Untuk mengubahnya menjadi 0 lagi maka R diberi pulsa kembali.

4. Keadaan HOLD .

Fllip Flop dinyatakan dalam keadaan Hold jika

data yang dimasukkan pada flip flop ditahan, hingga ada perubahan masukan.

Langkah langkah percobaan diatas adalah suatu cara untuk mengetahui prinsip

kerja dari flip flop secara bertahap dan terstruktur, dan dari percobaan

tersebut telah dibukrikan bahwa flip flop dapat menyimpan data dengan cara

menahan data tersebut.

Penahan NAND (NAND Latch)

Sebuah Flip Flop RS yang terbuat dari gerbang

logika NAND (NOT-AND) sering disebut sebagai penahan NAND. Penahan NAND prinsip

kerjanya sama dengan NOR. Perbedaannya terletak pada keadaan level atau tingkat

logikanya. Masukan – masuka SET dan RESET dari penahan NOR bekerja dari keadaan

O menjadi 1, sewaktu mengubah keadaan, sedangkan penahan NAND sebaliknya.

Masukan – masukan SET dan RESET dari penahan NAND bekerja dari keadaan 1 menjadi

0 sewaktu mengubah keadaan.

Penahan NAND dapat dinyatakan kembali dengan

teorema De Morgan, sehingga kita dapatkan rangkaian penahan yang lain tetapi

fungsi logikanya sama.

Penahan NAND juga dapat dibangun dengan gerbang

logika NAND silang (Cross NAND) dan disebut dengan Flip Flop SR NAND Silang

(Cross NAND SR Flip Flop)

Prinsip Kerja dari penahan NAND.

1. Keadaan Pengujian.

Apabila S = 1 (tinggi) maka keluaran Q akan

rendah. Walaupun R diubah-ubah keadaannya, keadaannya tetap 0.

2. Keadaan SET.

Apabila S berubah dari 1 menjadi 0, maka

keluaran Q akan langsung 1. Dan S hanya sekali saja membuat pulsa dari keadaan 0

menjadi 1. Sesudah itu jika keadaan S akan berubah ubah, keluaran tetap 1. Yang

artinya penahan NAND akan tetap menahan data pertama yang masuk, selama dalam

keadaan ini penahan NAND berada dalam keadaan HOLD

3. Keadaan RESET.

Pada keadaan ini, keluaran Q tetap 1 (tinggi)

apapun yang terjadi pada S. Cara menurunkan pulsa dari 1 menjadi 0 adalah

mengaktifkan R. Begitu R berubah keadaannya dari 1 menjadi 0 maka seketika itu

juga keluaran Q akan menjadi 0. Dan R hanya sekali saja berperan dalam mengubah

keadaan keluaran Q. Setelah itu apapun yang terjadi pada R tidak akan ditangga

pi oleh keluaran Q.

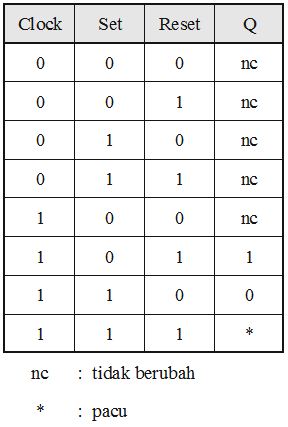

Flip Flop RS dikembangkan dengan ditambah

masukan untuk sinyal pendetak (clock), maka disebut Flip Flop RS Terdetak

(clocked SR flip flop). Flip Flop Terdetak bekerja dengan menggunakan sinya

pendetak. Pada hakikatnya prinsip keduanya sama, tetapi oerasi pengendalian

masukan dan keluarannya berbeda. Flip Flop RS terdetak ini harus menyesuaikan

diri dengan sinyal pendetak atau menyingkronkan diri dengan sinyal pendetak.

Apabila sinyal pendetak masukan pada logika 0, maka data yang masuk pada R dan S

tidak akan ditanggapi atau diproses oleh flip flop, sehingga keluaran Q tetap

tidak berubah. Jika sinyal pendetak berubah dari logika 0 menjadi 1, seketika

itu masukan SET dan RESET akan ditanggapi, sehingga keluaran Q berubah.

Pengoperasian flip flop SR terdetak disebut secara serempak atau sinkron.

Dinamakan sinkron karena bekerjanya menyesuaikan dengan irama waktu sinyal

pendetak.

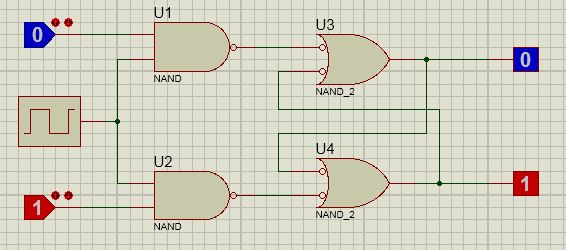

Rangkaian Flip Flop SR terdetak

Prinsip Kerja Flip Flop SR

Terdetak.

1. Pengujian Flip Flop.

Apabila masukan SET dalam keadaan logika 0 maka

keluaran Q akan 0. Kemudian masukan R diubah-ubah keadaannya, keluaran Q tidak

berubah yaitu tetap 0. Walaupun sinyal pendetak berubah-ubah level logikanya,

keluaran Q tetap tak berubah sedikitpun.

2. Keadaan SET.

Apabila masukan SET diberi pulsa maka pada

bagian masukan akan terjadi perubahan dari 0 menjadi 1. Tetapi keluaran Q akan

tetap 0. Flip Flop masih belum menanggapinya dan keluaran Q tetap tak berubah

(Q=0). Setelah sinyal pendetak tiba, saat itu juga flip flop akan menanggapinya

dan keluaran Q akan berubah menjadi 1. Dan S hanya sekali saja memberikan

pulsa,dari keadaan 0 menjadi 1. Sesudah itu jika keadaan S berubah-ubah,

keluaran Q akan tetap 1, meski sinyal penndetak berubah-ubah keadaannya.

3. Keadaan RESET.

Dengan melakukan pengujian diatas, flip flop

akan aktif. Keluaran Q adalah 1. Artinya flip flop sedang mengingat suatu tanda

biner, yaitu 1. Data biner tersebut akan tetap disimpan oleh flip flop

selamanya, tanpa batas waktu. Lalu, jika ingin mengubah data yang disimpan dalam

flip flop menjadi 0 atau keluaran Q=0. Caranya, masukan RESET diberi masukan

sinyal Flip flop tidak akan langsung menanggapinya dan memprosesnya tetapi

terlrbih dahulu sinyal pendetakya. Jika sinyal pendetak belum tiba atau masih

dalam keadaan 0, maka flip flop tidak akan berubah sedikitpun. Tetapi begitu

sinyal pendetak tiba, flip flop akan langsung menggapi dan keluaran Q akan

berubah menjadi 0. Jika masuka Reset diberi pulsa dan sinyal pendetal dalam

keadaan 1 maka masukan Reset akan langsung ditanggapi, dan keluaran Q akan 0.

Jika pada keluaran Q dipasang inverter maka keluaran Q’ akan 1. Masukan Reset

hanya memeiliki satu kesempatan untuk mengubah flip flop.

Tentang Sinyal

Pendetak.

Sinyal pendetak bekerja dalam suatu model atau

cara yang disebut Possitive Going Transition (PGT) atau Perubahan Tepi Naik

Positif. Artinya ketika denyut sinyal detak (clock) berganti dari 0 ke 1,

perubahan keadaan flip flop terjadi dan keluaran Q dan Q’ berubah. Keluaran

tepat pada tepi naik dari sinyal detak. Pada flip flop, masukan SET dan RESET

harus menunggu sampai sinyal pendetak menjadi logika 1, cara ini disebut dengan

pendekatan positif (positive clocking). Jika diantara masukan sinyal pencetak

dan gerbang – gerbang logika dipasang sebuah Inverter (gerbang NOT) akan didapat

pendekatan egatif (negative clocking)

Penahan D

Penahan D dapat dibuat dengan menggunakan

gerbang logika NAND seperti halnya rangkaian pada flip flop RS. Namun pada Flip

Flop D kita menggunankan tambahan Inverter sebelum gerbang NAND.

Prinsip kerja dari Flip

Flop D juga sederhana. Isyarat digital yang masuk pada D akan dibagi menjadi 2

jalur. Jalur pertama melewati inverter kemudian diteruskan pada gerbang NAND

yang menghasilkan Keluaran RESET, sedangkan jalur kedua langsung melewati

garbang NAND dan menghasilkan keluaran SET. Kemudian untuk masukan pada D, jika

masukan 0, maka gerbang NAND atas akan bernilai 0 dan gerbangn NAND bawah akan

bernilai 1 sehingga akan menghasilkan keluaran RESET. Namun jika masukan awal 1,

maka gerbang NAND atas akan bernilai 1 dan gerbang NAND bawah akan bernilai 0

sehingga akan menghasilkan keluaran SET. pada penahan D ini tidak akan terjadi

keadaan yang terpacu, karena gerbang logika yang digunakan menjamin untuk

mengeluarkan nilai SET dan RESET yang berlawanan

Penahan D dengan Sinyal Kendali Enable Tanpa Sinyal

Pendetak

Penahan D jenis ini dapat dibentuk dengan

menambahkan Inverter pada sebuah flip flop gerbang SR, rangkaian ini menggunakan

gerbang NOT, NAND dan Inverter. Untuk alur masukan data, SET mendapatkan masukan

langsung dari gerbang NOT yang terhubung langsung dengan masukan data kemudian

melewati gerbang NAND kemudian baru menghasilkan keluaran. Sedangkan untuk RESET

masukan yang sampai padanya telah melalui gerbang inverter dan gerbang NOT

sebelum sampai pada RESET, kemudian masukan diteruskan pada gerbang NAND sebelum

menghasilkan keluaran. Dalam penggunaannya masukan D dan keluaran Q akan selalu

sama selama Enable bernilai 1, namun saat Enable benilai 0 maka masukan D

terakhir yang terbaca saat Enable 1 akan ditahan, dan perubahan pada masukan D

tidak akan di proses.

Prinsip Kerja Penahan D

-

Flip Flop bekerja sebagai penahan data

-

Penahan D menyimpan data 1.

Penahan data ini berfungsi untuk menahan deretan pulsa biner

yang dimasukkan. Jika pada penahan D masukan enable bernilai 0 maka masukan yang

masuk itu akan ditahan dan disimpan hingga masukan enable diubah menjadi 1

kemudian keluaran Q akan tetap mengeluarkan keluaran 1 dan mengabaikan masukan

lain yang ada pada En dan D.

-

Penahan D menyimpan data 0.

Sinyal masukan awal yang diberikan pada masukan enable adalah

logika 1, kemudian pada masukan D diberi masukan 0, keluaran Q akan tetap

mengeluarkan masukan pertama yang telah di inputkan dengan mengabaikan perubahan

yang terjadi pada EN dan D

-

Flip flop bekerja

sebagai transparent data.

Jika

pada makukan En diberikan isyarat 1 yang dipanjar, maka keluaran Q yang

dihasilkan akan mengikuti perubahan masukkan pertama yang dimasukkan pada

penahan D. Sewaktu menjalankan penahan D dlam bentuk (mode) operasi ini, penahan

D dikatakan transparant atau bersifat tembus cahaya. Penahan D dapat dibangun

dengan menyusun gerbang logika seperti gamabar. Tetapi, penahan D akan lebih

cepat, mudah dan preaktis jika menggunakan rangkaian terpadu (IC). Dalam satu

kemasan chip terdapat beberapa penahan D dalam keadaan siap digunakan. Sedangkan

kode IC adalah IC TTL 7475. Setiap IC berisi 4 buah flip flop D

Tabel Fungsi untuk IC TTL

7475

Penahan D dengan Sinyal Pendetak

Cara mudah untuk memahami penahan D dengan

sinyal pendetak ini adalah dengan mengganti kendali Enable dangan sinyal

pendetak (clock). prinsip kerja dari penahan D dengan sinyal pendetak pun sama

dengan prinsip kerja penahan D dengan kendali Enable. Namun pada

pengoperasiannya terdapat sedikit perbedaan, jika ada penahan D dengan kendali

pendetak kita dapat mengendalikan batasan waktu, pada penahan D sinyal pendetak

kita harus mengikuti laju dari sinyal pendetak. Rangkaian D dengan sinyal

pendetak memiliki 2 masukan, yaitu masukan D dan detak (clock)

Jenis jenis Penahan D dengan sinyal pendetak

-

Penahan D dengan sinyal Pendetak sederhana

-

Penahan D Sinyal Pendetak

belum Aktif.

Saat sinyal

pendetak belum aktif maka masukan yang ada pada D ridak akan berpengaruh pada

keluaran Q

-

Penahan D Ketika Sinyal

Pendetak Aktif.

Pada saat

sinyal pendetak dalam keadaan 1, maka sinyal yang masuk pada D akan dibaca dalam

rentanagan masukan 1 pada sinyal pendetak, kemudian keadaan akhir dari sinyal D

yang dibaca akan ditahan. Namun jika pada saat sinyal pendetak telah mengalami

keadaan high namun sinal D tidak ada perubahan maka keluaran Q yang dihasilkan

pun tidak akan berubah.

-

Menghapus Isi Data pada

Penahan D.

Ada dua cara yang dapat dilakukan untuk melakukan pengubahan

keluaran Q yaitu dengan megubah sinyal penahan D menjadi 1 atau 0 pada saat

sinal pendetak bernilai 1

-

Penahan

D dlam Mode Operasi Mengikuti atau bersifat Transparent.

Kemudian ada kondisi dimana keluaran Q mengikuti sinyal yang

terdapat pada penahan D, kondisi ini disebut

transparent

-

Penahan D dengan pemicuan Tepi.

Flip Flop D pemicuan Tepi

Dapat dilihat dari diagram masukan bahwa pulsa biner 1 dan 2

yang masuk pada masukan D langsung di proses oleh penahan D. Tetapi ketika pulsa

biner 3 dan 4 masuk pada masukan D tidak ditanggapi sama sekali oleh penahan D.

Ini dikarenakan pulsa biner yang masuk yang dapat ditanggap i oleh penahan D

hanyalah pada tepi awal pulsa saja.Penahan D ini menggunakan rangkaian

Diferensito, rangkaian Diferensiator adalah sebuah rangkaian yang pada masukan

sinyal pendetaknya dipasang sebuah resistor dan kapasitor. Rangkaian Ini

dirancang agar sinyal pendetak yang dihasilkan lebih sempit dari sinyal pendetak

yang seharusnya terbentuk sehingga waktu cuplikannya menjadi lebih cepat. Sinyal

pendetak ini kemudian akan mengendalikan Penahan D menjadi Set atau Reset yang

mana reaksi yang dihasilkan akan lebih sensitif dari sinyal pendetak sebelumnya.

Perubahan ini dilakukan agar Flip Flop bereaksi pada perubahan awal pulsa naik

(tepi positif) dari sinyal detak

-

Penahan

D Pemicuan Tepi dengan Sinyal Pendetak dan Kendali Preset Clear.

Pada rangkaian ini, saat preset dan clear sama sama rendah,

maka akan dijumpai keadaan tidak aktif preset dan clear harus dalam tingkat

logika tinggi. bila preset dibuat rendah secara tersendiri, maka flip flop akan

di reset. Untuk lebih jelasnya kita masukkan pada sebuah contoh, misalnya sinyal

clear dapat berasal dari sebuah tombol tekan. Jadi, lepas dari keadaan sinyal

pendetakyang sedang bekerja, keluaran akan langsung di reset ketika operator

menekan tombol clear. Flip Flop D jenis ini mempunyai dua macam mode

pengoperasian, yaitu mode sinkron dan mode asinkron

Mode Pengoperasian

-

Penahan D Sinkron.

Pembacaan masukan pada Penahan D ini berpedoman tepi positif

dari clock yang aktif, jika data yang masuk pada masukan D bersamaan dengan tepi

positif dari clock maka keluaran yang muncul pada Q akan sejalan dengan masukan

pada D yang terbaca, sedangkan jika masukan pada D masuk tidak pada saat tepi

positif dari clock, maka keluaran Q yang dihasilkan nantinya tetap dari data

yang sejalan dengan tepi positif dari clock

-

Penahan D Asinkron.

Pengaktifan atau pembacaan masukan pada Penahan D Asinkron

tidak bergantung pada clock seperti Penahan D sinkron. Pengaktifan Penahan D

asinkron bergantung pada masukan Set dan Reset pada rangkaian. Saat Set bernilai

1 maka penahan D akan Aktif dan keluaran Q pun akan bernilai 1, dan saat Reset

benilai 1 maka Penahan Akan padam dan keluaran Q pun akan bernilai 0, meskipun

saat masukan 1 dari Reset masukan Set yang masih aktif akan diabaikan, namun

saat Set kembali bernilai 1 maka masukan Reset akan diabaikan.

Namun pada saat Set dan Reset sama sama dalam keadaan high,

maka penahan akan berada dalam keadaan pacu, ini adalah keadaan terlarang. Pada

prakteknya seperti pada LED, keadaan pacu dapat membuat LED redup atau berkedip

tidak beraturan.

-

Penahan

D Pemicuan Tepi dengan Rangkaian Tepi Gandengan Langsung.

Pada prinsipnya, rangkaina ini hanya menggapi sinyal masukan

untuk beberapa saat selama sinyal pendetak bertransmisi dari keadaan tinggi. Bit

data D disimpan rendah hanya pada waktu transisi naiknya sinyal

pendetak.

Flip flop JK merupakan flip flop yang paling ideal digunakan

sebagai piranti penyikpanan (memori).

Flip flop JK digunakan pada setiap komputer

digital maupun piranti lainnya. Dalam pemakaian bidang elektronika juga memiliki

banyak manfaat, misalnya :

- Pencacah frekuensi (frequency counter)

- Pembagi frekuensi (frequency divider)

- Pembangkit ragam gelombang kotak simetri (symetri square wave

form generator), dll.

Flip Flop JK dengan Pemicuan Tepi (Edge Triggered JK Flip

Flop)

Rangkaian dari flip flop ini terdiri dari

rangkaian gerbang logika, seperti flip flop lain. Tetapi, flip flop JK memilki

keunikan tersendiri, yaitu pada keluaran Q dan Q’ terdapat dua jenis umpan

balik, dengan keluaran yang diumpan balikkan kembali.

Ada dua jenis umpan balik :

-

Umpan Balik

flip flop. Berfungsi supaya rangkaian gerbang logika yang berada di dalam

garis putus – putus FL dapat menahan sebuah data biner.

-

Umpan

balik Togel (Toggle). Umpan balik ini enyebabkan flip flop JK mengalami

toggle.

Selain terdapt dua jenis umpan balik, flip flop

JK memiliki 2 masukan kendali, yang disebut dengan masukan J dan K. Masukan J

dan K berfungsi mengatur apa yang akan dilakukan rangkaian pada tepi sinyal

pendetak. pada bagian masukan dari pendetak dibei rangkaian Diferensator, namun

dalam Chip IC tidak digunakan rangkaian RC tetapi gerbang Not dan And, karena

pada IC, komponen RC memakan Tempat dan kurang praktis.

Pinsip Kerja Flip Flop JK

-

Keadaan tidak Aktif.

Ini adalah keadaan dimana sinyal J dan K bernilai 0 sehingga

juga menghasilkan masukan Q bernilai 0

-

Keadaan SET.

Ini

terjadi disaat sinyal pada masukan J bernilai 1 dan masukan K bernilai 0

sehingga dihasilkan keluaran Q bernilai 1, pada saat ini lah Flip Flop

dinyatakan dalam keadaan SET

-

Keadaan RESET.

Ini terjadi disaat sinyal pada masukan J bernilai 0 dan

masukan K bernilai 1 sehingga dihasilkan keluaran Q bernilai 0, pada saat ini

lah Flip Flop dinyatakan dalam keadaan RESET

-

Keadaan Toggle.

Ini terjadi saat masukan J dan K sama sama berniali 1

sehingga dihasilkan keadaan set dan reset yang terus

bergantian

Flip Flop JK dengan Pemicuan Tepi Negatif

Flip Flop JK dengan Pemicuan Tepi Negatif

memiliki prinsip kerja yang sama dengan tipe sebelumnya, yang berbeda hanya pada

pemicu yang digunakan saling berlawanan. Biasanya data yang diterima adalah

perubahan pulsa ke rendah (tepi negatif), cara pemasukan data J dan K seperti

ini dibuat dengan merancang flip flop agar emiliki kemampuan untuk dapat

menerima data masukan kendali masukan J dan K dari tepi sinyal pendetak.

D.DASAR

SHIFT REGISTER

Dasar dari register

geser adalah menggeser data informasi yang disimpan di dalam register geser

tersebut. Sebagai contoh, register geser dengan 4-bit akan menggeser data biner

yang saling berurutan sebanyak 4 posisi atau kita sebut 4 bit.

Proses bergesernya

data yang masuk ke dalam sebuah

register terjadi

sejalan dengan sinyal pendetak. Cepat atau lambatnya suatu pewaktuan dalam

pergeseran ditentukan oleh sebuah sinyal pendetak yang digunakan dalam rangkaian

tersebut. Setiap kali sinyal pendetak berdenyut, maka data yang tersimpan akan

digeser satu posisi. Jika pulsa pendetak tersebut berdenyut sekali lagi, maka

data yang tersimpan akan digeser satu posisi lagi dan seterusnya

CONTOH REGISTER

GESER

Contoh kasus

register geser dalam sehari-hari yaitu terdapat pada kalkulator yang biasa kita

gunakan. Bila kita memasukan masing-masing digit yang ada pada papan tombol,

angka pada peraga akan bergeser ke kiri. Jadi, untuk memasukkan angka 268 kita

harus mengerjakan hal berikut.

Pertama, kita akan

menekan dan melepaskan 2 pada papan tombol kalkulator, maka 2 muncul pada layar

dengan posisi paling kanan. Selanjutnya, kita menekan dan melepaskan 6 pada

papan tombol yang dapat menyebabkan 2 bergeser satu posisi ke kiri, yang

kemudian memungkinkan 6 muncul pada posisi paling kanan layar, 26 muncul pada

layar. Kemudian, kita menekan dan melepaskan 8 pada papan tombol, 268 muncul

pada layar.

JENIS - JENIS

REGISTER GESER

Ada 4 jenis

register geser, yaitu:

Serial Input Serial

Output (SISO)

Serial Input

Paralel Output (SIPO)

Paralel In Serial

Output (PISO)

Paralel Input

Paralel Output (PIPO)